# A new architecture for mini-computers— The DEC PDP-11

by G. BELL,\* R. CADY, H. McFARLAND, B. DELAGI, J. O'LAUGHLIN and R. NOONAN

Digital Equipment Corporation Maynard, Massachusetts

and

W. WULF

Carnegie-Mellon University Pittsburgh, Pennsylvania

# INTRODUCTION

1

The mini-computer\*\* has a wide variety of uses: communications controller; instrument controller; largesystem pre-processor; real-time data acquisition systems...; desk calculator. Historically, Digital Equipment Corporation's PDP-8 Family, with 6,000 installations has been the archetype of these minicomputers.

In some applications current mini-computers have limitations. These limitations show up when the scope of their initial task is increased (e.g., using a higher level language, or processing more variables). Increasing the scope of the task generally requires the use of more comprehensive executives and system control programs, hence larger memories and more processing. This larger system tends to be at the limit of current mini-computer capability, thus the user receives diminishing returns with respect to memory, speed efficiency and program development time. This limitation is not surprising since the basic architectural concepts for current mini-computers were formed in the early 1960's. First, the design was constrained by cost, resulting in rather simple processor logic and register configurations. Second, application experience was not available. For example, the early constraints often created computing designs with what we now consider weaknesses:

- 1. limited addressing capability, particularly of larger core sizes

- 2. few registers, general registers, accumulators, index registers, base registers

- 3. no hardware stack facilities

- 4. limited priority interrupt structures, and thus slow context switching among multiple programs (tasks)

- 5. no byte string handling

- 6. no read only memory facilities

- 7. very elementary I/O processing

<sup>\*\*</sup> The PDP-11 design is predicated on being a member of one (or more) of the micro, midi, mini, ..., maxi (computer name) mark ts. We will define these names as belonging to computers of the third generation (integrated circuit to medium scale integrated circuit technology), having a core memory with cycle time of  $.5 \sim 2$  microseconds, a clock rate of  $5 \sim 10$  Mhz..., a single processor with interrupts and usually applied to doing a particular task (e.g., controlling a memory or communications lines, pre-processing for a larger system, process control). The specialized names are defined as follows:

|       | maximum addressable<br>primary memory (words) | processor and<br>memory cost<br>(1970 kilodollars) | word<br>length<br>(bits) | processor<br>state<br>(words) | data types                                     |

|-------|-----------------------------------------------|----------------------------------------------------|--------------------------|-------------------------------|------------------------------------------------|

| micro | 8 K                                           | $\sim 5$                                           | $8\sim 12$               | 2                             | integers, words, boolean vectors               |

| mini  | 32 K                                          | $5\sim 10$                                         | $12\sim 16$              | 2-4                           | vectors (i.e., indexing)                       |

| midi  | $65\sim 128~{ m K}$                           | $10\sim 20$                                        | $16\sim 24$              | 4-16                          | double length floating point<br>(occasionally) |

<sup>\*</sup> Also at Carnegie-Mellon University, Pittsburgh, Pennsylvania.

- 8. no larger model computer, once a user outgrows a particular model

- 9. high programming costs because users program in machine language.

In developing a new computer the architecture should at least solve the above problems. Fortunately, in the late 1960's integrated circuit semiconductor technology became available so that newer computers could be designed which solve these problems at low cost. Also, by 1970 application experience was available to influence the design. The new architecture should thus lower programming cost while maintaining the low hardware cost of mini-computers.

The DEC PDP-11. Model 20 is the first computer of a computer family designed to span a range of functions and performance. The Model 20 is specifically discussed, although design guidelines are presented for other members of the family. The Model 20 would nominally be classified as a third generation (integrated circuits), 16-bit word, 1 central processor with eight 16-bit general registers, using two's complement arithmetic and addressing up to  $2^{16}$  eight bit bytes of primary memory (core). Though classified as a general register processor, the operand accessing mechanism allows it to perform equally well as a 0-(stack), 1-(general register) and 2-(memory-to-memory) address computer. The computer's components (processor, memories, controls, terminals) are connected via a single switch, called the Unibus.

The machine is described using the PMS and ISP notation of Bell and Newell (1970) at different levels. The following descriptive sections correspond to the levels: external design constraints level; the PMS level—the way components are interconnected and allow information to flow; the program level or ISP (Instruction Set Processor)—the abstract machine which interprets programs; and finally, the logical design level. (We omit a discussion of the circuit level—the PDP-11 being constructed from TTL integrated circuits.)

# DESIGN CONSTRAINTS

The principal design objective is yet to be tested; namely, do users like the machine? This will be tested both in the market place and by the features that are emulated in newer machines; it will indirectly be tested by the life span of the PDP-11 and any offspring.

# Word length

The most critical constraint, word length (defined by IBM) was chosen to be a multiple of 8 bits. The memory word length for the Model 20 is 16 bits, although there are 32- and 48-bit instructions and 8and 16-bit data. Other members of the family might have up to 80 bit instructions with 8-, 16-, 32-and 48-bit data. The internal, and preferred external character set was chosen to be 8-bit ASCII.

## Range and performance

Performance and function range (extendability) were the main design constraints; in fact, they were the main reasons to build a new computer. DEC already has (4) computer families that span a range\* but are incompatible. In addition to the range, the initial machine was constrained to fall within the small-computer product line, which means to have about the same performance as a PDP-8. The initial machine outperforms the PDP-5, LINC, and PDP-4 based families. Performance, of course, is both a function of the instruction set and the technology. Here, we're fundamentally only concerned with the instruction set performance because faster hardware will always increase performance for any family. Unlike the earlier DEC families, the PDP-11 had to be designed so that new models with significantly more performance can be added to the family.

A rather obvious goal is maximum performance for a given model. Designs were programmed using benchmarks, and the results compared with both DEC and potentially competitive machines. Although the selling price was constrained to lie in the \$5,000 to \$10,000 range, it was realized that the decreasing cost of logic would allow a more complex organization than earlier DEC computers. A design which could take advantage of medium- and eventually large-scale integration was an important consideration. First, it could make the computer perform well; and second, it would extend the computer family's life. For these reasons, a general registers organization was chosen.

## Interrupt response

Since the PDP-11 will be used for real time control applications, it is important that devices can communicate with one another quickly (i.e., the response time of a request should be short). A multiple priority level, nested interrupt mechanism was selected; additional priority levels are provided by the physical position of a device on the Unibus. Software polling is

Ĺ

<sup>\*</sup> PDP-4, 7, 9, 15 family; PDP-5, 8, 8/S, 8/I, 8/L family; LINC, PDP-8/LINC, PDP-12 family; and PDP-6, 10 family. The initial PDP-1 did not achieve family status.

unnecessary because each device interrupt corresponds to a unique address.

# Software

The total system including software is of course the main objective of the design. Two techniques were used to aid programmability: first benchmarks gave a continuous indication as to how well the machine interpreted programs; second, systems programmer continually evaluated the design. Their evaluation considered: what code the compiler would produce; how would the loader work; ease of program relocability; the use of a debugging program; how the compiler, assembler and editor would be coded—in effect, other benchmarks; how real time monitors would be written to use the various facilities and present a clean interface to the users; finally the ease of coding a program.

# Modularity

Structural flexibility (sometimes called modularity) for a particular model was desired. A flexible and straightforward method for interconnecting components had to be used because of varying user needs (among user classes and over time). Users should have the ability to configure an optimum system based on cost, performance and reliability, both by interconnection and, when necessary, constructing new components. Since users build special hardware, a computer should be easily interfaced. As a by-product of modularity, computer components can be produced and stocked, rather than tailor-made on order. The physical structure is almost identical to the PMS structure discussed in the following section; thus, reasonably large building blocks are available to the user.

# **Microprogramming**

A note on microprogramming is in order because of current interest in the "firmware" concept. We believe microprogramming, as we understand it (Wilkes, 1951), can be a worthwhile technique as it applies to processor design. For example, microprogramming can probably be used in larger computers when floating point data operators are needed. The IBM System/360 has made use of the technique for defining processors that interpret both the System/360 instruction set and earlier family instruction sets (e.g., 1401, 1620, 7090). In the PDP-11 the basic instruction set is quite straightforward and does not necessitate microprogrammed interpretation. The processor-memory connection is asynchronous and therefore memory of any speed can be connected. The instruction set encourages the user to write reentrant programs; thus, read-only memory can be used as part of primary memory to gain the permanency and performance normally attributed to microprogramming. In fact, the Model 10 computer which will not be further discussed has a 1024-word read only memory, and a 128-word read-write memory.

# Understandability

Understandability was perhaps the most fundamental constraint (or goal) although it is now somewhat less important to have a machine that can be quickly understood by a novice computer user than it was a few years ago. DEC's early success has been predicated on selling to an intelligent but inexperienced user. Understandability, though hard to measure, is an important goal because all (potential) users must understand the computer. A straightforward design should simplify the systems programming task; in the case of a compiler, it should make translation (particularly code generation) easier.

# PDP-11 STRUCTURE AT THE PMS LEVEL\*

# Introduction

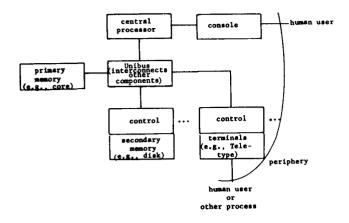

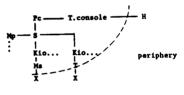

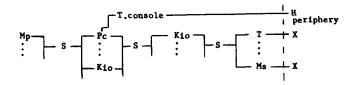

PDP-11 has the same organizational structure as nearly all present day computers (Figure 1). The primitive PMS components are: the primary memory (Mp) which holds the programs while the central processor (Pc) interprets them; io controls (Kio) which manage data transfers between terminals (T) or secondary memories (Ms) to primary memory (Mp); the components outside the computer at periphery (X) either humans (H) or some external process (e.g., another computer); the processor console (T. console) by which humans communicate with the computer and observe its behavior and affect changes in its state: and a switch (S) with its control (K) which allows all the other components to communicate with one another. In the case of PDP-11, the central logical switch structure is implemented using a bus or chained switch (S) called the Unibus, as shown in Figure 2. Each physical component has a switch for placing messages on the bus or taking messages off the bus. The central control decides the next component to

<sup>\*</sup> A descriptive (block-diagram) level (Bell and Newell, 1970) to describe the relationship of the computer components: processors memories, switches, controls, links, terminals and data operators.

Conventional block diagram

PMS diagram

#### PMS Notation

| <u>form</u><br>Component/X                                                                                                                                   | <pre>comment<br/>name X is an alias (abbreviation<br/>for a component is separated by /)</pre>                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| a := b                                                                                                                                                       | a is assigned the meaning of b                                                                                  |

| I                                                                                                                                                            | delimits mutually exclusive alter-<br>matives                                                                   |

| Components := (Processor/P  <br>Memory/N Switch/S <br>Control/K[Termins1/T]<br>Dets operation/D[Limk/L]<br>Humma/E)                                          | set of primitive components and<br>their abbreviations                                                          |

| X(a <sub>1</sub> :v <sub>1</sub> ; a <sub>2</sub> :v <sub>2</sub> ; a <sub>n</sub> :v <sub>b</sub> )                                                         | n sttribute/s, vslus/v psirs.<br>Attribute may be omitted if it<br>can be inferred from dimensions<br>of value. |

| index number/#                                                                                                                                               | attribute giving component number                                                                               |

| name/'                                                                                                                                                       | attribute giving component name                                                                                 |

| miscellaneous abbreviations :- (<br>Mp/primery memory Ms/secondary memory [Pc/c<br>Kig/io control]Pio/io processor]s/sec/secc<br>b/bit[w/word]i/information] | entral processor <br>mds char/character                                                                         |

|                                                                                                                                                              | information carrying link<br>(bi-directions1)                                                                   |

| → <del>←</del>                                                                                                                                               | uni-directional information<br>cerrying links                                                                   |

|                                                                                                                                                              | delimits alternatives                                                                                           |

## Figure 1—Conventional block diagram and PMS diagram of PDP-11

use the bus for a message (call). The S (Unibus)differs from most switches because any component can communicate with any other component.

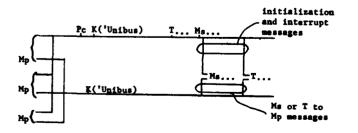

The types of messages in the PDP-11 are along the

lines of the hierarchical structure common to present day computers. The single bus makes conventional and other structures possible. The message processes in the structure which utilize S(Unibus) are:

- 1. The central processor (Pc) requests that data be read or written from or to primary memory (Mp) for instructions and data. The processor calls a particular memory module by concurrently specifying the module's address, and the address within the modules. Depending on whether the processor requests reading or writing, data is transmitted either from the memory to the processor or vice versa.

- 2. The central processor (Pc) controls the initialization of secondary memory (Ms) and terminal (T) activity. The processor sets status bits in the control associated with a particular Ms or T, and the device proceeds with the specified action (e.g., reading a card, or punching a character into paper tape). Since some devices transfer data vectors directly to primary memory, the vector control information (i.e., the memory location and length) is given as initialization information.

- 3. Controls request the processor's attention in the form of interrupts. An interrupt request to the processor has the effect of changing the state of the processor; thus the processor begins executing a program associated with the interrupting process. Note, the interrupt process is only a signaling method, and when the processor interruption occurs, the interruptee specifies a unique address value to the processor. The address is a starting address for a program.

- 4. The central processor can control the transmission of data between a control (for T or Ms) and either the processor or a primary memory for program controlled data transfers. The device signals for attention using the interrupt dialogue and the central processor responds by managing the data transmission in a fashion similar to transmitting initialization information.

<sup>1</sup> Unibus control packaged with Pc

Figure 2-PDP-11 physical structure PMS diagram

- 5. Some device controls (for T or Ms) transfer data directly to/from primary memory without central processor intervention. In this mode the device behaves similar to a processor; a memory address is specified, and the data is transmitted between the device and primary memory.

- 6. The transfer of data between two controls, e.g., a secondary memory (disk) and say a terminal/T. display is not precluded, provided the two use compatible message formats.

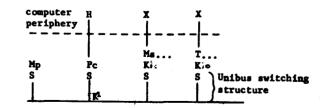

As we show more detail in the structure there are, of course, more messages (and more simultaneous activity). The above does not describe the shared control and its associated switching which is typical of a magnetic tape and magnetic disk secondary memory systems. A control for a DECtape memory (Figure 3) has an S('DECtape bus) for transmitting data between

Figure 3-DECtape control switching PMS diagram

a single tape unit and the DECtape transport. The existence of this kind of structure is based on the relatively high cost of the control relative to the cost of the tape and the value of being able to run concurrently with other tapes. There is also a dialogue at the periphery between X-T and X-Ms which does not use the Unibus. (For example, the removal of a magnetic tape reel from a tape unit or a human user (H) striking a typewriter key are typical dialogues.)

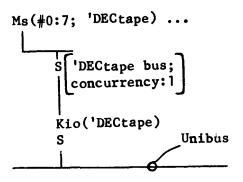

All of these dialogues lead to the hierarchy of present computers (Fig. 4). In this hierarchy we can see the paths by which the above messages are passed (Pc-Mp; Pc-K; K-Pc; Kio-T and Kio-Ms; and Kio-Mp; and, at the periphery, T-X and T-Ms; and T.console-H).

# Model 20 implementation

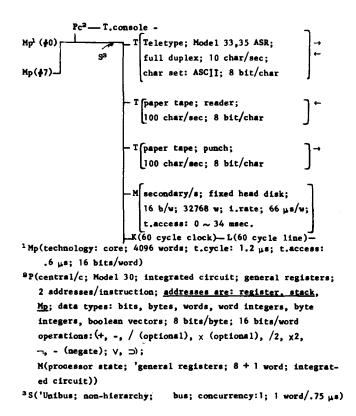

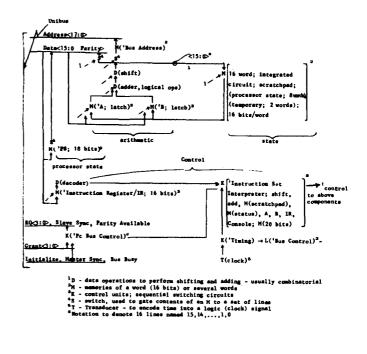

Figure 5 shows the detailed structure of a uniprocessor, Model 20 PDP-11 with its various

Figure 4—Conventional hierarchy computer structure

components (options). In Figure 5 the Unibus characteristics are surpressed. (The detailed properties of the switch are described in the logical design section.)

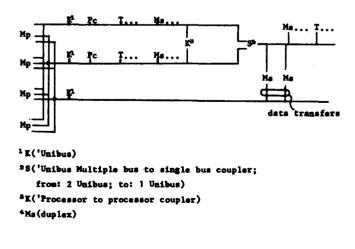

## Extensions to increase performance

The reader should note (Figure 5) that the important limitations of the bus are: a concurrency of one, namely, only one dialogue can occur at a given time, and a maximum transfer rate of one 16-bit word per .75  $\mu$ sec., giving a transfer rate of 21.3 megabits/second. While the bus is not a limit for a uni-processor structure, it is a limit for multiprocessor structures. The bus also imposes an artificial limit on the system performance when high speed devices (e.g., TV cameras, disks) are

Figure 5-PDP-11 structure and characteristics PMS diagram

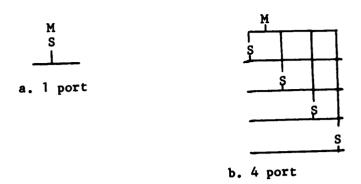

transferring data to multiple primary memories. On a larger system with multiple independent memories the supply of memory cycles is 17 megabits/second times the number of modules. Since there is such a large supply of memory cycles/second and since the central processor can only absorb approximately 16 megabits/ second, the simple one Unibus structure must be modified to make the memory cycles available. Two changes are necessary: first, each of the memory modules have to be changed so that multiple units can access each module on an independent basis; and second, there must be independent control accessing mechanisms. Figure 6 shows how a single memory is modified to have more access ports (i.e., connect to 4 Unibusses).

Figure 7 shows a system with 3 independent memory modules which are accessed by 2 independent Unibusses. Note that two of the secondary memories and one of the transducers are connected to both Unibusses. It should be noted that devices which can potentially interfere with Pc-Mp accesses are constructed with two ports; for simple systems, the two ports are both connected to the same bus, but for systems with more busses, the second connection is to an independent bus.

Figure 7-Three Mp, 2 S('Unibus) structure PMS diagram

Figure 8 shows a multiprocessor system with two central processors and three Unibusses. Two of the Unibus controls are included within the two processors. and the third bus is controlled by an independent control unit. The structure also has a second switch to allow either of two processors (Unibusses) to access common shared devices. The interrupt mechanism allows either processor to respond to an interrupt and similarly either processor may issue initialization information on an anonymous basis. A control unit is needed so that two processors can communicate with one another; shared primary memory is normally used to carry the body of the message. A control connected to two Pc's (see Figure 8) can be used for reliability; either processor or Unibus could fail, and the shared Ms would still be accessible.

## Higher performance processors

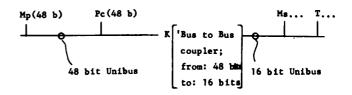

Increasing the bus width has the greatest effect on performance. A single bus limits data transmission to 21.4 megabits/second, and though Model 20 memories are 16 megabits/second, faster (or wider) data path width modules will be limited by the bus. The Model 20 is not restricted, but for higher performance processors operating on double word (fixed point) or triple word (floating point) data two or three accesses are required for a single data type. The direct method to improve the performance is to double or triple the primary memory and central processor data path widths. Thus, the bus data rate is automatically doubled or tripled.

For 32- or 48-bit memories a coupling control unit is needed so that devices of either width appear isomorphic to one another. The coupler maps a data

Figure 8-Dual Pc multiprocessor system PMS diagram

request of a given width into a higher- or lower-width request for the bus being coupled to, as shown in Figure 9. (The bus is limited to a fixed number of devices for electrical reasons; thus, to extend the bus a bus repeating unit is needed. The bus repeating control unit is almost identical to the bus coupler.) A computer with a 48-bit primary memory and processor and 16-bit secondary memory and terminals (transducers) is shown in Figure 9.

In summary, the design goal was to have a modular structure providing the final user with freedom and flexibility to match his needs. A secondary goal of the Unibus is open-endedness by providing multiple busses and defining wider path busses. Finally, and most important, the Unibus is straightforward.

# THE INSTRUCTION SET PROCESSOR (ISP) LEVEL-ARCHITECTURE\*

## Introduction, background and design constraints

The Instruction Set Processor (ISP) is the machine defined by hardware and/or software which interprets programs. As such, an ISP is independent of technology and specific implementations.

The instruction set is one of the least understood aspects of computer design; currently it is an art. There is currently no theory of instruction sets, although there have been attempts to construct them (Maurer, 1966), and there has also been an attempt to have a computer program design an instruction set (Haney, 1968). We have used the conventional approach in this design: first a basic ISP was adopted and then incremental design modifications were made (based on the results of the benchmarks).\*\* Although the approach to the design was conventional, the resulting machine is not. A common classification of processors is as zero-, one-, two-, three-, or three-plus-one-address machines. This scheme has the the form:

$$op \ l1, \ l2, \ l3, \ l4$$

where l1 specifies the location (address) in which to store the result of the binary operation (op) of the contents of operand locations l2 and l3, and l4 specifies the location of the next instruction.

The action of the instruction is of the form:

$$l1 \leftarrow l2 \ op \ l3; \ goto \ l4$$

The other addressing schemes assume specific values for one or more of these locations. Thus, the oneaddress von Neumann (Burks, Goldstine and von Neumann, 1946) machines assume l1 = l2 = the "accumulator" and l4 is the location following that of the current instruction. The two-address machine assumes l1 = l2; l4 is the next address.

Historically, the trend in machine design has been to move from a 1 or 2 word accumulator structure as in the von Neumann machine towards a machine with accumulator and index register(s).\* As the number of registers is increased the assignment of the registers to specific functions becomes more undesirable and inflexible; thus, the general-register concept has developed. The use of an array of general registers in the processor was apparently first used in the firstgeneration, vacuum-tube machine, PEGASUS (Elliott et al., 1956) and appears to be an outgrowth of both 1- and 2-address structures. (Two alternative structures-the early 2- and 3-address per instruction computers may be disregarded, since they tend to always access primary memory for results as well as temporary storage and thus are wasteful of time and memory cycles, and require a long instruction.) The stack concept (zero-address) provides the most efficient

Figure 9—Computer with 48 bit Pc, Mp with 16 bit Ms, T PMS diagram

<sup>\*</sup> The word architecture has been operationally defined (Amdahl, Blaauw and Brooks, 1964) as "the attributes of a system as seen by a programmer, i.e., the conceptual structure and functional behavior, as distinct from the organization of the data flow and controls, the logical design and the physical implementation." \*\* A predecessor multiregister computer was proposed which used a similar design process. Benchmark programs were coded on each of 10 "competitive" machines, and the object of the design was to get a machine which gave the best score on the benchmarks. This approach had several fallacies: the machine had no basic character of its own; the machine was difficult to program since the multiple registers were assigned to specific functions and had inherent idiosyncrasies to score well on the benchmarks; the machine did not perform well for programs other than those used in the benchmark test; and finally, compilers which took addvantage of the machine appeared to be difficult to write. Since all "competitive machines" had been hand-coded from a common flowchart rather than separate flowcharts for each machine, the apparent high performance may have been due to the flowchart organization.

<sup>\*</sup> Due in part to needs, but mainly technology which dictates how large the structure can be.

access method for specifying algorithms, since very little space, only the access addresses and the operators, needs to be given. In this scheme the operands of an operator are always assumed to be on the "top of the stack". The stack has the additional advantage that arithmetic expression evaluation and compiler statement parsing have been developed to use a stack effectively. The disadvantage of the stack is due in part to the nature of current memory technology. That is, stack memories have to be simulated with random access memories, multiple stacks are usually required, and even though small stack memories exist, as the stack overflows, the primary memory (core) has to be used.

Even though the trend has been toward the general register concept (which, of course, is similar to a two address scheme in which one of the addresses is limited to small values), it is important to recognize that any design is a compromise. There are situations for which any of these schemes can be shown to be "best". The IBM System/360 series uses a general register structure, and their designers (Amdahl, Blaauw and Brooks, 1964) claim the following advantages for the scheme:

- 1. Registers can be assigned to various functions: base addressing, address calculation, fixed point arithmetic and indexing.

- 2. Availability of technology makes the general registers structure attractive.

The System/360 designers also claim that a stack organized machine such as the English Electric KDF 9 (Allmark and Lucking, 1962) or the Burroughs B5000 (Lonegran and King, 1961) has the following disadvantages:

- 1. Performance is derived from fast registers, not the way they are used.

- 2. Stack organization is too limiting and requires many copy and swap operations.

- 3. The overall storage of general registers and stack machines are the same, considering point #2.

- 4. The stack has a bottom, and when placed in slower memory there is a performance loss.

- 5. Subroutine transparency is not easily realized with one stack.

- 6. Variable length data is awkward with a stack.

We generally concur with points 1, 2, and 4. Point 5 is an erroneous conclusion, and point 6 is irrelevant (that is, general register machines have the same problem). The general-register scheme also allows processor implementations with a high degree of parallelism since instructions of a local block all can operate on several registers concurrently. A set of truly general purpose registers should also have additional uses. For example, in the DEC PDP-10, general registers are used for address integers, indexing, floating point, boolean vectors (bits), or program flags and stack pointers. The general registers are also addressable as primary memory, and thus, short program loops can reside within them and be interpreted faster. It was observed in operation that PDP-10 stack operations were very powerful and often used ((accounting for as many as 20% of the executed instructions, in some programs, e.g., the compilers.)

The basic design decision which sets the PDP-11 apart was based on the observation that by using *truly* general registers and by suitable addressing mechanisms it was possible to consider the machine as a zero-address (stack), one-address (general register), or two-address (memory-to-memory) computer. Thus, it is possible to use whichever addressing scheme, or mixture of schemes, is most appropriate.

Another important design decision for the instruction set was to have only a few data types in the basic machine, and to have a rather complete set of operations for each data type. (Alternative designs might have more data types with few operations, or few data types with few operations.) In part, this was dictated by the machine size. The conversion between data types must be easily accomplished either automatically or with 1 or 2 instructions. The data types should also be sufficiently primitive to allow other data types to be defined by software (and by hardware in more powerful versions of the machine). The basic data type of the machine is the 16 bit integer which uses the two's complement convention for sign. This data type is also identical to an address.

## PDP-11 model 20 instruction set (basic instruction set)

A formal description of the basic instruction set is given in Appendix 1 using the ISPL notation (Bell and Newell, 1970). The remainder of this section will discuss the machine in a conventional manner.

## **Primary memory**

The primary memory (core) is addressed as either  $2^{16}$  bytes or  $2^{15}$  words using a 16 bit number. The linear address space is also used to access the inputoutput devices. The device state, data and control registers are read or written like normal memory locations.

## **General register**

The general registers are named:  $R[0:7]\langle 15:0 \rangle^*$ ; that is, there are 8 registers each with 16 bits. The naming is done starting (at the left with bit 15 (the sign bit) to the least significant bit 0. There are synonyms for R[6] and R[7]:

Stack Pointer/SP(15:0) := R[6](15:0)

used to access a special stack which is used to store the state of interrupts, traps and subroutine calls

Program Counter/PC(15:0) := R[7](15:0)

points to the current instruction being interpreted. It will be seen that the fact that PC is one of the general registers is crucial to the design.

Any general register, R[0:7], can be used as a stack pointer. The special Stack Pointer (SP) has additional properties that force it to be used for changing processor state interrupts, traps, and subroutine calls (It also can be used to control dynamic temporary storage subroutines.)

In addition to the above registers there are 8 bits used (from a possible 16) for processor status, called  $PS\langle 15.0 \rangle$  register. Four bits are the Condition Codes (CC) associated with arithmetic results; the T-bit controls tracing; and three bits control the priority of running programs Priority  $\langle 2:0 \rangle$ . Individual bits are mapped in PS as shown in Appendix 1.

# Data types and primitive operations

There are two data lengths in the basic machine: bytes and words, which are 8 and 16 bits, respectively. The non-trivial data types are word length integers (w.i.); byte length integers (by .i); word length boolean vectors (w.bv), i.e., 16 independent bits (booleans) in a 1 dimensional array; and byte length boolean vectors (by.bv). The operations on byte and word boolean vectors are identical. Since a common use of a byte is to hold several flag bits (booleans), the operations can be combined to form the complete set of 16 operations. The logical operations are: "clear," "complement," "inclusive or," and "implication" ( $x \supseteq y$  or  $\neg x \lor y$ ).

There is a complete set of arithmetic operations for the word integers in the basic instruction set. The arithmetic operations are: add, subtract, multiply (optional), divide (optional), compare, add one, subtract one, clear, negate, and multiply and divide by

۱

powers of two (shift). Since the address integer size is 16 bits, these data types are most important. Byte length integers are operated on as words by moving them to the general registers where they take on the value of word integers. Word length integer operations are carried out and the results are returned to memory (truncated).

The floating point instructions defined by software (not part of the basic instruction set) require the definition of two additional data types (of length two and three), i.e., double word (d.w.) and triple (t.w.) words. Two additional data types, double integer (d.i.) and triple floating point (t.f. or f) are provided for arithmetic. These data types imply certain additional operations and the conversion to the more primitive data types.

## Address (operand) calculation

The general methods provided for accessing operands are the most interesting (perhaps unique) part of the machine's structure. By defining several access methods to a set of general registers, to memory, or to a stack (controlled by a general register), the computer is able to be a 0, 1 and 2 address machine. The encoding of the instruction Source (S) fields and Destination (D) fields are given in Fig. 10 together with a list of the various access modes that are possible. (Appendix 1 gives a formal description of the effective address calculation process.)

It should be noted from Figure 10 that all the common access modes are included (direct, indirect, immediate, relative, indexed, and indexed indirect) plus several relatively uncommon ones. Relative (to PC) access is used to simplify program loading, while immediate mode speeds up execution. The relatively uncommon access modes, auto-increment and autodecrement, are used for two purposes: access to a stack under control of the registers\* and access to bytes or words organized as strings or vectors. The indirect access mode allows a stack to hold addresses of data (instead of data). This mode is desirable when manipulating longer and variable-length data types (e.g., strings, double fixed and triple floating point). The register auto increment mode may be used to access a byte string; thus, for example, after each access, the register can be made to point to the next data item. This is used for moving data blocks, searching for particular elements of a vector, and bytestring operations (e.g., movement, comparisons, editing).

<sup>\*</sup> A definition of the ISP notation used here may be found in Appendix 1.

<sup>\*</sup>Note, by convention a stack builds toward register 0, and when the stack crosses  $400_8$ , a stack overflow occurs.

<sup>1</sup>address increment/ai value is 1 or 2

Figure 10-Address calculation formats

This addressing structure provides flexibility while retaining the same, or better, coding efficiency than classical machines. As an example of the flexibility possible, consider the variations possible with the most trivial word instruction MOVE (see Figure 11). The MOVE instruction is coded as it would appear in conventional 2-address, 1-address (general register) and 0-address (stack) computers. The two-address format is particularly nice for MOVE, because it provides an efficient encoding for the common operation:  $A \leftarrow B$  (note, the stack and general registers are not involved). The vector move  $A[I] \leftarrow B(I)$  is also efficiently encoded. For the general register (and 1-address format), there are about 13 MOVE operations that are commonly used. Six moves can be encoded for the stack (about the same number found in stack machines).

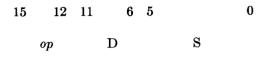

## **Instruction formats**

There are several instruction decoding formats depending on whether 0, 1, or 2 operands have to be explicitly referenced. When 2 operands are required, they are identified as Source/S and Destination/D and the result is placed at Destination/D. For single operand instructions (unary operators) the instruction action is  $D \leftarrow u D$ ; and for two operand instructions (binary operators) the action is  $D \leftarrow D$  b S (where u and b are unary and binary operators, e.g.,  $\neg$ , - and +, -,  $\times$ , /, respectively. Instructions are specified by a 16-bit word. The most common binary operator format (that for operations requiring two addresses) is shown below.

The other instruction formats are given in Figure 12.

#### Instruction interpretation process

The instruction interpretation process is given in Figure 13, and follows the common fetch-execute cycle. There are three major states: (1) interrupting the PC and PS are placed on the stack accessed by the Stack Pointer/SP, and the new state is taken from an address specified by the source requesting the trap or interrupt; (2) trace (controlled by T-bit)—essentially one instruction at a time is executed as a trace

| Assembler Format                              | Effect                              | Description                                                            |

|-----------------------------------------------|-------------------------------------|------------------------------------------------------------------------|

| Two Address Nachine forme                     | t:                                  |                                                                        |

| HOVE B,A <sup>1</sup>                         | A ← B                               | replace A with contents of B                                           |

| HOVE #1,A                                     | A ← H                               | replace A with number, N                                               |

| HOVE B(RZ), A(RZ)                             | $A[I] \leftarrow B[I]$              | replace element of a connector                                         |

| MOVE (R <sub>3</sub> ) +, (R <sub>4</sub> ) + | A[I] ← B[I];<br>I ← I + 1           | replace element of a vector,<br>move to mext element                   |

| General Register Machine :                    | format:                             |                                                                        |

| HOVE A,R1                                     | R1A                                 | load register                                                          |

| HOVE R1, A                                    | A - R}                              | store register                                                         |

| HOVE GA,R1                                    | R1 ← M[A]                           | load or store indirect vis<br>element A                                |

| HOVE R1, R3                                   | R1 ← R3                             | register to register transfer                                          |

| HOVE R1, A(BZ)                                | A[I] ← B1                           | store indemsd (load indemsd)<br>(or store)                             |

| NOVE (A(RO),R1                                | $R1 \leftarrow H[A[1]]$             | load (or store) indexed indirect                                       |

| HOVE (R1), R3                                 | R1 ← H[R2]                          | load indirect via register                                             |

| HOVE (R1) +, R3                               | N3 ← M[I]                           | lond (or store) element indirect<br>via register, move to mext element |

| Stack Machine format:                         |                                     |                                                                        |

| HOVE (H, -(Lo)                                | 8 ⊷ #                               | load stack with literal                                                |

| HOVE A, -(R0)                                 | <b>5</b> ← A                        | load stack with contents of A                                          |

| HOVE @(R0)+, -(R0)                            | \$ ← H[\$]                          | load stack with unnory specified<br>by top of stack                    |

| HOVE (Ro)+, A                                 | A 🛏 B                               | store stack in A                                                       |

| HOVE (R0)+, @(R0)+                            | H[8 <sub>2</sub> ] ← 8 <sub>1</sub> | store stack top in memory<br>addressed by stack top -1                 |

| HOVE (Ro), -(Ro)<br>Assembler formet:         | 8 - 8                               | duplicate top of stack                                                 |

| () denotes contents of                        | memory addressed by                 |                                                                        |

| <ul> <li>decrement register f</li> </ul>      | first                               |                                                                        |

| + increment register a                        | fter                                |                                                                        |

| @ indirect<br># literel                       |                                     |                                                                        |

| 4 TTPATAT                                     |                                     |                                                                        |

# Figure 11—Coding for the MOVE instruction to compare with conventional machines

14

Binary arithmetic and logical operations: bop S יים form: D ← S b D example: ADD (:=bop=0010)  $\rightarrow$  (CC,D  $\leftarrow$  D+S); Unary arithmetic and logical operation: uop D form: D ← u D: examples: NEG (:=uop=0000101100) → (CC,D ← - D) - negate ASL (:=uop=00000110011)  $\rightarrow$  (CC, D  $\leftarrow$  D x 2); shift left Branch (relative) operators: brop offset form: <u>if</u> brop condition <u>then</u> (PC ← PC + offset); example: BEQ (: = brop =  $03_{16}$ ) (Z  $\rightarrow$  (PC  $\leftarrow$  PC + offset)): 0 000 000 001 D form: PC ← D + Pc to subroutine: 0 000 100 save R[sr] on stack, enter AP D + PC Misc. operations: op code form: ST ← f example: HALT (: = instruction = 0)  $\rightarrow$  (RUN  $\leftarrow$  0);

<sup>1</sup>Mote: these instructions are all 1 word. D snd/or S may each require 1 additional immediate data or address word. Thus instructions can be 1, 2, or 3 words long.

Figure 13—PDP-11 instruction interpretation process state diagram

trap occurs after each instruction, and (3) normal instruction interpretation. The five (lower) states in the diagram are concerned with instruction fetching, operand fetching, executing the operation specified by the instruction and storing the result. The non-trivial details for fetching and storing the operands are not shown in the diagram but can be constructed from the effective address calculation process (Appendix 1). The state diagram, though simplified, is similar to 2- and 3-address computers, but is distinctly different than a 1 address (1 accumulator) computer.

The ISP description (Appendix 1) gives the operation of each of the instructions, and the more conventional diagram (Fig. 12) shows the decoding of instruction classes. The ISP description is somewhat incomplete; for example, the add instruction is defined as: ADD (:= bop = 0010)  $\rightarrow$  (CC,D  $\leftarrow$  D + S); addition does not exactly describe the changes to the Condition Codes/CC (which means whenever a binary opcode [bop] of 0010<sub>2</sub> occurs the ADD instruction is executed with the above effect). In general, the CC are based on the result, that is, Z is set if the result is zero, N if negative, C if a carry occurs, and V if an overflow was detected as a result of the operation. Conditional branch instructions may thus follow the arithmetic instruction to test the results of the CC bits.

# Examples of addressing schemes

# Use as a stack (zero address) machine

Figure 14 lists typical zero-address machine instructions together with the PDP-11 instructions which perform the same function. It should be noted that translation (compilation) from normal infix expressions to reverse Polish is a comparatively trivial task. Thus, one of the primary reasons for using stacks is for the evaluation of expressions in reverse Polish form.

Consider an assignment statement of the form

$$D \leftarrow A + B/C$$

which has the reverse Polish form

$DABC/+ \leftarrow$

and would normally be encoded on a stack machine as follows

load stack address of D load stack A load stack B load stack C / + store

| Common stack instruction:Equivalent PDP-11 instruction:place address value A on stackHOVE $AA$ , $-(RO)^1$ load stack from memory address specifiedHOVE $AA$ , $-(RO)$ isod stack from memory address specifiedHOVE $A$ , $-(RO)$ store stack at memory address specifiedHOVE $A$ , $-(RO)$ store stack at memory address specifiedHOVE $(RO)+$ , $\oplus(RO)+$ by stackHOVE $(RO)+$ , $\oplus(RO)+$ store stack at memory location AHOVE $(RO)+$ , $\oplus(RO)+$ duplicate top of stackHOVE $(RO)+$ , $\oplus(RO)$ +, add 2 top data of stack to stackADD $(RO) +$ , $\oplus RO$ -, x, /; subtract, multiply, divide(see add)-; negate top data of stackNEG $\oplus RO$ 2 top data of stackSET $(RO)+$ , $\oplus RO$ -; complement top of stackCOM $\oplus RO$ test top of stack (set branch indicators)SET $(RO)+$ , $RI$ branch on indicatorJUHPadd addressed location A to top of stack -HOVE $(RO)+$ , $RI$ hove $(RO)+$ , $RI$ , $(RO)+$ , $RI$ HOVE $(RO)+$ , $RI$ HOVE $(RO)+$ , $RI$ HOVE $(RO)+$ , $RI$ HOVE $(RO)+$ , $RO$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|

| load stack from memory address specified<br>by stackMOVE $\otimes (RO)+$ , $= (RO)$ load stack from memory location AMOVE $A$ , $-(RO)$ store stack at memory address specified<br>by stackMOVE $(RO)+$ , $\oplus (RO)+$ store stack at memory location AMOVE $(RO)+$ , $\oplus (RO)+$ duplicate top of stackMOVE $(RO)+$ , $A$ duplicate top of stackMOVE $(RO)+$ , $A$ -, x, /; subtract, multiply, divide(see add)-; negate top data of stackNEG $\oplus RO$ clear top data of stackCLE $\oplus RO$ $2$ top data of stackCLE $\oplus RO$ $\gamma_i$ "icclusive or" 2 top data of stack "and"SEET $(RO)+$ , $\oplus RO$ $2$ top data of stackCOM $\oplus RO$ $\gamma_i$ "icclusive or" 2 top data of stack "and"SEET $(RO)+$ , $\oplus RO$ $2$ top data of stackCOM $\oplus RO$ $\gamma_i$ complement top of stackTST $\oplus RO$ branch on indicatorBR $(=, A, >, z, <, s)$ jump unconditionalJUHPadd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack dataMOVE $(RO)+$ , $R2$<br>MOVE $R, RO$ MOVE $R, RO$ <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Common stack instruction:                 | Equivalent PDF-II instruction: |

| by stack<br>load stack from memory location A<br>store stack at memory address specified<br>by stack<br>store stack at memory address specified<br>by stack<br>store stack at memory location A<br>duplicate top of stack<br>+, add 2 top data of stack to stack<br>-, x, /; subtract, multiply, divide<br>-; negate top data of stack<br>clear top data of stack<br>v; "inclusive or" 2 top data of stack "and"<br>2 top data of stack<br>-; complement top of stack<br>test top of stack (set branch indicators)<br>branch on indicator<br>jump unconditional<br>add addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack data<br>reset stack location to N<br>MOYE (RO)+, ⊕(RO)<br>MOYE (RO)+, ⊕(RO)+, ⊕(RO)<br>MOYE (RO)+, ⊕(RO)+, ⊕(RO)+, ⊕(RO)+, ⊕(RO)+, ⊕ | place address value A on stack            | MOVE 🗛 = (RO)                  |

| store stack at memory address specifiedNOVE $(R0)+$ , $\oplus(R0)+$ by stackstore stack at memory location ANOVE $(R0)+$ , Aduplicate top of stackHOVE $(R0)+$ , Aduplicate top of stackADD $(R0) +$ , $\oplus R0$ -, x, /; subtract, multiply, divide(see add)-; negate top data of stackNEG $\oplus R0$ Clear top data of stackCLR $\oplus R0$ 2 top data of stackSET $(R0)+$ , $\oplus R0$ 2' top data of stackCDM $\oplus R0$ 2 top data of stackSET $(R0)+$ , $\oplus R0$ 2 top data of stackCOM $\oplus R0$ 2 top of stack (set branch indicators)TST $\oplus R0$ branch on indicatorJUHPadd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack dataHOVE $(R0)+$ , R1<br>HOVE $(R0)+$ , R2<br>HOVE $R2, -(R0)$ reset stack location to NCOM $\oplus R0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           | MOVE ●(R0)+, - (R0)            |

| by stack<br>store stack as memory location A<br>duplicate top of stack<br>+, add 2 top data of stack to stack<br>-, x, /; subtract, multiply, divide<br>-; negate top data of stack to stack<br>Clear top data of stack<br>v; "inclusive or" 2 top data of stack "and"<br>2 top data of stack<br>-; complement top of stack<br>test top of stack (set branch indicators)<br>branch on indicator<br>jump unconditional<br>add addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack data<br>reset stack location to N<br>HOVE (R0)+, A<br>MOVE (R0)+, A<br>MOVE (R0)+, A<br>MOVE (R0)+, A<br>MOVE (R0)+, A<br>MOVE (R0)+, A<br>MOVE (R0)+, R1<br>HOVE (R0)+, R2<br>HOVE (R0)-, CR0<br>HOVE R2, -(R0)<br>HOVE R2, -(R0)<br>HOVE R4, R0<br>COH GR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | load stack from memory location A         | MOVE A, -(RO)                  |

| duplicate top of stackMOVE (R0), -(R0)+, add 2 top data of stack to stackADD (R0) +, @R0-, x, /; subtract, multiply, divide(see add)-; negate top data of stackNEG @R0clear top data of stackCLR @R0y, "inclusive or" 2 top data of stackSSET (R0)+, @R0-; complement top of stackCCH @R0-; complement top of stack (set branch indicators)TST @R0branch on indicatorBR (=, $4$ , >, $2$ , <, $\leq$ )jump unconditionalJUHPadd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: loed stack, add swap top 2 stack dataMOVE (R0)+, R1<br>HOVE (R0)+, R2<br>HOVE R2, -(R0)<br>HOVE R2, -(R0)reset stack location to NOCH @R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           | HOVE (R0)+, ⊕(R0)+             |

| +, add 2 top data of stack to stackADD (R0) +, $\mathfrak{GRO}$ -, x, /; subtract, multiply, divide(see add)-; negate top data of stackNEG $\mathfrak{GRO}$ clear top data of stackCLR $\mathfrak{GRO}$ v; "inclusive or" 2 top data of stackBSET (R0)+, $\mathfrak{GRO}$ 2 top data of stackCLR $\mathfrak{GRO}$ -; complement top of stackCOH $\mathfrak{GRO}$ test top of stack (set branch indicators)TST $\mathfrak{GRO}$ branch on indicatorBR (=, $4$ , >, $2$ , <, $\leq$ )jump unconditionalJUMPadd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack dataMOVE (R0)+, R1<br>HOVE (R0)+, R2<br>HOVE R2, - (R0)<br>HOVE R2, - (R0)reset stack location to NCOH $\mathfrak{GRO}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | store stack as memory location A          | MOVE (R0)+, A                  |

| -, x, /; subtract, multiply, divide(see add)-, x, /; subtract, multiply, divide(see add)-; negate top data of stackNEG @R0clear top data of stackCLR @R02 top data of stackBSET (R0)+, @R02 top data of stackCOM @R0-; complement top of stackCOM @R0test top of stack (set branch indicators)TST @R0branch on indicatorBR (=, $\neq$ , >, $\geq$ , <, $\leq$ )jump unconditionalJUMPadd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack dataMOVE (R0)+, R1<br>MOVE (R0)+, R2<br>HOVE (R0)+, R2<br>HOVE R2, - (R0)<br>MOVE R2, - (R0)reset stack location to NCOM @R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | duplicate top of stack                    | MOVE (R0), -(R0)               |

| NEG @R0c:act top data of stackNEG @R0c:lear top data of stackCLR @R02 top data of stackBSET (R0)+, @R02 top data of stackCOM @R0c:st top of stack (set branch indicators)TST @R0branch on indicatorTST @R0jump unconditionalJUMPadd addressed location A to top of stack -<br>to: load stack, add swap top 2 stack dataADD A, @R0reset stack location to NNOVE (R0)+, R1<br>HOVE (R0)+, R2<br>HOVE R2, -(R0)reset stack location to NCOM @R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | + , add 2 top data of stack to stack      | ADD (R0) +, 🗰                  |

| clear top data of stackCLR $\oplus RO$ V; "inclusive or" 2 top data of stackBSET (RO)+, $\oplus RO$ 2 top data of stackBSET (RO)+, $\oplus RO$ 2 top data of stackCOM $\oplus RO$ 2 top of stack (set branch indicators)TST $\oplus RO$ branch on indicatorBR (=, #, >, ≥, <, ≤)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -, x, /; subtract, multiply, divide       | (see add)                      |

| Content top the top of stack "and"BSET (R0)+, @R02 top data of stackCOM @R02 top data of stackCOM @R0-; complement top of stackTST @R0branch on indicatorBR ( $-, \neq, >, z, <, s$ )jump unconditionalJUHPadd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack dataMOVE (R0)+, R1<br>HOVE (R0)+, R2<br>HOVE R2, -(R0)<br>HOVE R2, -(R0)reset stack location to NNOVE ##, R0<br>COM @R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -; negate top data of stack               | NEG ORO                        |

| 2 top data of stack       CON @R0         -; complement top of stack       CON @R0         test top of stack (set branch indicators)       TST @R0         branch on indicator       BR (=, $\neq$ , >, >, >, <, <)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | clear top data of stack                   | CLR RO                         |

| TST $(0,0)$ test top of stack (set branch indicators)branch on indicatorjump unconditionaladd addressed location A to top of stack -<br>(not common for stack machine) equivalent<br>to: load stack, add swap top 2 stack dataMOVE $(R_0)+$ , R1<br>HOVE $(R_0)+$ , R2<br>HOVE $(R_0)-$ , $(R_0)$<br>HOVE $(R_0)-$<br>R2, $-$ (R0)<br>HOVE $R_2$ , $-$ (R0)<br>HOVE $R_2$ , $-$ (R0)<br>HOVE $R_2$ , $-$ (R0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                           | BSET (R0)+, ØR0                |